基于FPGA的RFID阅读器设计

作者:张捍东 张淳

来源:RFID世界网

日期:2009-07-14 10:29:38

摘要:作为一项具有广泛应用前景的技术,RFID阅读器近年来已在多个领域发挥了重要作用。由于单片机的开发周期长且批量小,因此,采用FPGA为核心来设计高频、远距离的阅读器。经验证,它能够快速、准确地实现曼彻斯特编码的译码并进行CRC校验。设计的通用异步收发器实现了数据的接收和发送,具有电路形式简单、移植方便等优点。

0 引言

RFID(radio frequency identification)即射频识别技术,是自动识别技术的一种,主要由阅读器和电子标签两部分组成。通过无线射频方式进行非接触双向数据通信,对目标加以识别并获取相关数据。

阅读器的设计是RFID系统设计中的关键部分,关于它的设计方案有很多种。FPGA是大规模可编程器件中的另一大类PLD(programmable logic device)器件,既继承了ASIC的大规模、高集成度、高可靠性的优点,又克服了普通ASIC设计周期长、投资大、灵活性差的缺点,逐步成为复杂数字硬件电路设计的首选。因此,本文设计了一种基于FPGA的高频、远距离RFID阅读器。

1 系统功能概述

ISO/IEC 18000-6是ISO/IEC 18000标准的一部分,它定义了工作在高频率范围内(860~960 MHz)射频识别系统的空气接口和通信协议Ⅲ,并规定了Type A和Type B两类非接触式射频卡,如表1所示。

表1 两类射频卡的比较

阅读器的工作原理是:标签接收到阅读器的响应帧后,将NRZ码编码成Manchester码,并调制上载波后发送出去,阅读器的高频接口将该信息解调,即将载波信号滤除后,输出Manchester码到译码模块;译码模块将译码得到的NRZ码串行输出到通用异步收发器UART的接收模块;接收模块将其转化为并行数据,送人并行CRC(cyclic redundancy check)模块,UART发送模块等待数据帧发送命令XMIT_CMD,当CRC模块检查到接收的数据正确,便将XMIT_CMD置为“1” ,发送模块开始发送数据。

2 阅读器设计方案

对目标芯片EP1 C6Q240C8,采用Quartus II开发软件,使用VHDL语言完成对阅读器各模块的描述,并且调用第三方仿真工具ModelSim来进行时序仿真。Quartus II是Ahera公司的综合性PLD开发软件,支持原理图、VHDL、Verilog—HDL等多种设计输入形式,内嵌自有的综合器以及仿真器,还可以调用第三方仿真工具完成从设计输人到硬件配置的完整PLD设计流程。Quaaus II的设计步骤为设计输入、设计编译、功能仿真、时序仿真、硬件配置。

2.1 译码模块

从电子标签到阅读器的数据传输可采用Manehester编码,这将有利于发现传输中的错误。因为在比特长度内,“没有变化”的状态是不允许的。当多个标签同时发送的数据位有不同值时,接收的上升沿和下降沿互相抵消,由于该状态是不允许的,所以阅读器利用该错误就可以判定碰撞发生的具体位置。在曼彻斯特编码中,某比特位的值是由该比特长度内半个比特周期时的电平的变化(上升/下降)来表示的,从“1”跳变到“0”表示二进制“1”,从“0”跳变到“1”表示二进制“0”。

阅读器的工作频率为915 MHz,Manchester码的传送频率为915 MHz/16。其基本设计原理是采用915 MHz作为基准时钟clk ,利用分频器得到基准时钟的16分频(clk/16)和8分频(clk/8)。用2个D触发器构成移位寄存器,输人时钟为(clk/8),将输入的Manchester码并行移出,并行移出的2个值为q1和q0。再构造一个比较器,采用clk/16作为输入时钟,这样就能将Manchester码在一个比特长度内的两个电平值进行比较,如果q0=“1”,q1 =“0”,就输出二进制“1”;如果qo=“0”,q1=“1”,就输出二进制“0”。这样就实现了Manchester码的译码。

采用QuartusⅡ开发软件,可以观察到设计的RTL视图,如图3所示。其中mdi为输入的Manchester码,Out。为输出的译码。

表2 占用芯片资源情况表

1001”;Out1为得到的八位二进制译码“11011010”。输出的译码比输入的Manchester码延时一个周期。译出八位二进制码的时间仅为156.264 ns。因此,本设计能达到快速准确译码的目的,且占用资源少。

2.2 通用异步收发器接收模块

接收器模块接收译码模块输出的串行二进制码。

并将其转化为并行数据输出。接收状态机共有R_START(等待起始位)、R_CENTER(求中点)、R_WAIT(等待采样)、R_SAMPLE(采样)和R_STOP(停止)这5个状态,如图5所示。

2.3 并行CRC模块

通常,CRC采用线性反馈移位寄存器的串行实现,本文采用一种并行CRC运算方法。CRC校验码采用多项式:x16 + x12 + x5 +1。使用16个移位寄存器,每次输入8 bits数据,相当于一次并行运算就得到了串行移位运算时需要8次移位得到的结果,具有更高的处理速度,缩短了阅读器对卡的响应时间。

2.4 通用异步收发器发送模块

当发送模块处于X_START状态时,发送一个位时间宽度的逻辑0至输出TXD ,紧接着状态机转入X_WAIT状态。XCNT16是balk的计数器。X_WAIT状态和接收状态机中的R_WAIT状态相似。计数器记到15时,转入X_SHIFT状态,实现待发数据的并串转换,转换完成回到X_WAIT状态。当数据帧发送完毕,状态机进入X_STOP状态,等待另一个数据帧的发送命令。

3 下载配置

EP1C6Q240C8芯片支持被动串行和JTAG两种下载模式 ,这里采用JTAG模式对芯片进行配置。下载电缆与电路板相连的是10针插座,采用1O个小方格来表示,配置电路如图6所示(其中nCE0悬空,DA-TA。和DCLK使用高电平或低电平驱动)。

FPGA是简化SoC设计的一种新选择,省略了单片机的许多附件部分。本文实现了基于ISO/IEC18000-6标准阅读器的解码、处理和发送功能。通过实验证明,本设计具有解码速度快、接收数据准确、识别率高等优点。

RFID(radio frequency identification)即射频识别技术,是自动识别技术的一种,主要由阅读器和电子标签两部分组成。通过无线射频方式进行非接触双向数据通信,对目标加以识别并获取相关数据。

阅读器的设计是RFID系统设计中的关键部分,关于它的设计方案有很多种。FPGA是大规模可编程器件中的另一大类PLD(programmable logic device)器件,既继承了ASIC的大规模、高集成度、高可靠性的优点,又克服了普通ASIC设计周期长、投资大、灵活性差的缺点,逐步成为复杂数字硬件电路设计的首选。因此,本文设计了一种基于FPGA的高频、远距离RFID阅读器。

1 系统功能概述

ISO/IEC 18000-6是ISO/IEC 18000标准的一部分,它定义了工作在高频率范围内(860~960 MHz)射频识别系统的空气接口和通信协议Ⅲ,并规定了Type A和Type B两类非接触式射频卡,如表1所示。

表1 两类射频卡的比较

Tab.1 Comparison of 2 types of radio frequency m odules

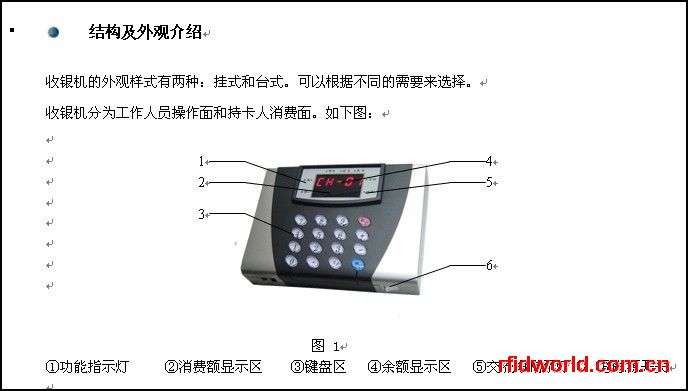

图1 标签响应帧格式

Fig.1 Response format ofthe tag

图2 阅读器结构图

Fig.2 Structural diagram of the reader

阅读器的工作原理是:标签接收到阅读器的响应帧后,将NRZ码编码成Manchester码,并调制上载波后发送出去,阅读器的高频接口将该信息解调,即将载波信号滤除后,输出Manchester码到译码模块;译码模块将译码得到的NRZ码串行输出到通用异步收发器UART的接收模块;接收模块将其转化为并行数据,送人并行CRC(cyclic redundancy check)模块,UART发送模块等待数据帧发送命令XMIT_CMD,当CRC模块检查到接收的数据正确,便将XMIT_CMD置为“1” ,发送模块开始发送数据。

2 阅读器设计方案

对目标芯片EP1 C6Q240C8,采用Quartus II开发软件,使用VHDL语言完成对阅读器各模块的描述,并且调用第三方仿真工具ModelSim来进行时序仿真。Quartus II是Ahera公司的综合性PLD开发软件,支持原理图、VHDL、Verilog—HDL等多种设计输入形式,内嵌自有的综合器以及仿真器,还可以调用第三方仿真工具完成从设计输人到硬件配置的完整PLD设计流程。Quaaus II的设计步骤为设计输入、设计编译、功能仿真、时序仿真、硬件配置。

2.1 译码模块

从电子标签到阅读器的数据传输可采用Manehester编码,这将有利于发现传输中的错误。因为在比特长度内,“没有变化”的状态是不允许的。当多个标签同时发送的数据位有不同值时,接收的上升沿和下降沿互相抵消,由于该状态是不允许的,所以阅读器利用该错误就可以判定碰撞发生的具体位置。在曼彻斯特编码中,某比特位的值是由该比特长度内半个比特周期时的电平的变化(上升/下降)来表示的,从“1”跳变到“0”表示二进制“1”,从“0”跳变到“1”表示二进制“0”。

阅读器的工作频率为915 MHz,Manchester码的传送频率为915 MHz/16。其基本设计原理是采用915 MHz作为基准时钟clk ,利用分频器得到基准时钟的16分频(clk/16)和8分频(clk/8)。用2个D触发器构成移位寄存器,输人时钟为(clk/8),将输入的Manchester码并行移出,并行移出的2个值为q1和q0。再构造一个比较器,采用clk/16作为输入时钟,这样就能将Manchester码在一个比特长度内的两个电平值进行比较,如果q0=“1”,q1 =“0”,就输出二进制“1”;如果qo=“0”,q1=“1”,就输出二进制“0”。这样就实现了Manchester码的译码。

采用QuartusⅡ开发软件,可以观察到设计的RTL视图,如图3所示。其中mdi为输入的Manchester码,Out。为输出的译码。

图3 译码模块的RTL视图

Fig.3 RTL view of the decode block

表2 占用芯片资源情况表

Tab.2 The used chip resources

图4 译码仿真波形

Fig.4 Decod e simulation wavcform

1001”;Out1为得到的八位二进制译码“11011010”。输出的译码比输入的Manchester码延时一个周期。译出八位二进制码的时间仅为156.264 ns。因此,本设计能达到快速准确译码的目的,且占用资源少。

2.2 通用异步收发器接收模块

接收器模块接收译码模块输出的串行二进制码。

并将其转化为并行数据输出。接收状态机共有R_START(等待起始位)、R_CENTER(求中点)、R_WAIT(等待采样)、R_SAMPLE(采样)和R_STOP(停止)这5个状态,如图5所示。

图5 UART接收器的接收状态机

Fig.5 Receiving status principle of UART

2.3 并行CRC模块

通常,CRC采用线性反馈移位寄存器的串行实现,本文采用一种并行CRC运算方法。CRC校验码采用多项式:x16 + x12 + x5 +1。使用16个移位寄存器,每次输入8 bits数据,相当于一次并行运算就得到了串行移位运算时需要8次移位得到的结果,具有更高的处理速度,缩短了阅读器对卡的响应时间。

2.4 通用异步收发器发送模块

当发送模块处于X_START状态时,发送一个位时间宽度的逻辑0至输出TXD ,紧接着状态机转入X_WAIT状态。XCNT16是balk的计数器。X_WAIT状态和接收状态机中的R_WAIT状态相似。计数器记到15时,转入X_SHIFT状态,实现待发数据的并串转换,转换完成回到X_WAIT状态。当数据帧发送完毕,状态机进入X_STOP状态,等待另一个数据帧的发送命令。

3 下载配置

EP1C6Q240C8芯片支持被动串行和JTAG两种下载模式 ,这里采用JTAG模式对芯片进行配置。下载电缆与电路板相连的是10针插座,采用1O个小方格来表示,配置电路如图6所示(其中nCE0悬空,DA-TA。和DCLK使用高电平或低电平驱动)。

图6 配置电路图

Fig.6 Circuit diagram of configuration

FPGA是简化SoC设计的一种新选择,省略了单片机的许多附件部分。本文实现了基于ISO/IEC18000-6标准阅读器的解码、处理和发送功能。通过实验证明,本设计具有解码速度快、接收数据准确、识别率高等优点。

登录

登录

注册

注册