一文读懂28GHz 5G通信频段射频前端模块

随着 5G 毫米波预期即将进入商用,行业内关键公司的研发正在顺利推进,已经完成定制组件指标划定、设计和验证。实现未来毫米波 5G 系统所需的基本组件是射频前端模块(FEM)。该模块包括发射机的最终放大级以及接收机中最前端的放大级以及发射 / 接收开关(Tx/Rx)以支持时分双工(TDD)。FEM 必须在发射模式下具备高线性度,并在接收模式下具备低噪声系数。由于毫米波 5G 系统可能需要用户终端采用多个 FEM 构成相控阵架构或开关天线波束架构。因此 FEM 必须采用高效、紧凑和低成本的方式实现,且最好能简单控制和监测。

本文介绍了符合以上所有要求的 28GHz 5G 通信频段(27.5 至 28.35GHz)射频前端模块 MMIC(单片微波集成电路)的设计、实现和验证。该射频前端由 Plextek RFI 公司开发,采用 WINSemiconductors(稳懋半导体)的 PE-15 4V 电压、0.15μm、增强型 GaAs PHEMT 工艺实现。它采用紧凑型低成本且兼容 SMT(表贴)安装的 5mm x 5mm 二次注塑兼容 QFN 封装,适用于大批量、低成本的制造。它涵盖 27 至 29GHz,因此支持完整的 28GHz 5G 频段。

1. 设计目标

FEM 发射通道的设计着重于功率回退下实现高效率,以提供线性放大,这是 5G 通信系统提出的要求。功率回退下的目标功率附加效率(PAE)定为 6%,三阶交调(IMD3)低于 -35dBc(功率回退值:从 1dB 压缩点开始大约退回 7dB)。对应 1dB 压缩点(P1dB)的 RF 输出功率定为 20dBm。而接收通道需要在非常低的电流消耗下(最大 15mA,+4V 电源),实现低于 4dB 的噪声系数(包括开关损耗)。

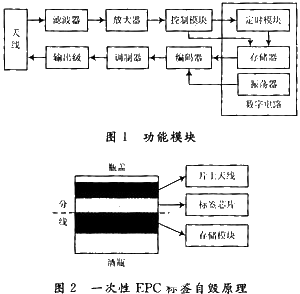

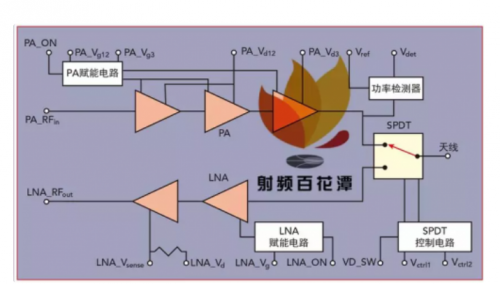

射频前端 MMIC 的功能框图如图 1 所示。发送信号路径从图的上半部分中的左侧延伸到右侧;输入端口位于标有“PA_RFin”的引脚上。输入信号由三级功放(PA)放大,然后通过 RF 功率检测器和单刀双掷(SPDT)开关连接至天线。片上定向功率检测器可监测发射出的射频输出功率,并且片上集成了温度补偿功能。带补偿的功率检测器输出由电压“Vref”和电压“Vdet”之间的差值决定。芯片内集成了由(低电平有效)逻辑信号“PA_ON”控制的快速开关赋能电路(图 1 中的 PA 赋能电路)。可在发射和接收模式之间切换时,快速给 PA 上电和断电,从而在 PA 不用时达到仅使用 0.1mA 的电流,最大限度地提高整个系统的效率。

图 1:28GHz 5G 通信射频前端模块芯片的功能框图

PA 通常会工作在从压缩点回退几 dB 的条件下,以保持其发射的调制信号不严重失真。设计方法是优化功率放大器工作在 P1dB 点回退 7dB 左右的性能。为了在该工作条件下达到较优的 PAE,PA 将偏置在深 AB 类。

2. 设计折中策略

该设计起始于对候选单元晶体管进行器件级仿真。这项仿真工作可以获得如器件尺寸、偏置点、目标阻抗、PA 级数和驱动器比率等关键信息,为后续精细的功率放大器设计奠定了坚实的基础。

这项工作的一个重要部分在于确定如何最大限度地提高功率回退下的 PAE。一般来说,可通过降低器件静态偏置电流密度来实现。但是该方法中电流密度可往下调的范围受限于增益和线性度约束,因为这两者都随着电流密度的降低而恶化。功率回退条件下的 PAE 和增益与线性度之间有明确的折中关系。

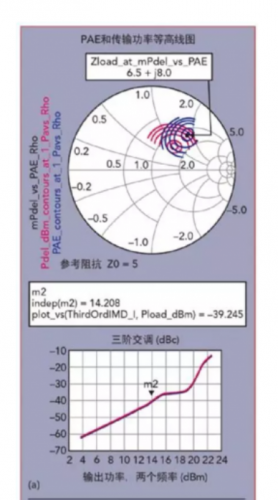

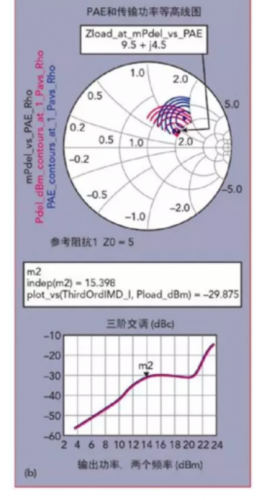

设计中主要关心的线性度指标是在功率回退条件下,IMD3 必须小于 -35dBc。如图 2 所示,在偏置电流降低的情况下,IMD3 性能对基频负载条件特别敏感。图 2a 显示了偏置为深 AB 类的 8×50μm 器件在 4V、75mA/mm 时的负载牵引仿真结果,并标出了 P1dB 下的 PAE 最佳点对应的负载。该图还给出了仿真所得该最佳负载和功率回退条件下 IMD3 的性能,表明离 -35dBc 的指标还有大约 4dB 的裕度。仿真的 PAE 在该功率回退条件下约为 15%,且该效率只计入器件的作用,不包括任何输出损耗。图 2b 显示了相同器件和偏置工作条件下,P1dB 功率最佳点对应的负载以及 IMD3 等信息。发现在相同的相对功率回退情况下,其 IMD3 的性能明显更差,超出指标 5dB 以上,而此时 PAE 和前一种条件相似,约为 15.7%。

图 2:P1dB 条件下最佳 PAE 对应的阻抗点以及对应的功率回退条件下的 IMD3(a);P1dB 条件下最佳功率对应的阻抗点以及对应的功率回退条件下的 IMD3(b)。

进一步评估了史密斯圆图上的其他阻抗点下,功放的 P1dB 和功率回退两种条件下的性能。图 2a 中的负载条件明显具有最好的综合性能,因此被选定用于输出级设计。最终选择了 52mA/mm 的偏置电流,并选择了 8x50μm 器件作为输出级的基本单元,以满足功率指标要求。并根据总的传输增益指标确定了需要三级放大。

通过依次为驱动放大级和预驱动放大级选择最佳晶体管尺寸来设计完整的三级功率放大器。这同样需要仔细考虑设计折中,因为较大的晶体管尺寸可改善整体线性度但会降低 PAE。当所有晶体管的尺寸和偏置确定后,就可以继续进行匹配和偏置电路的详细设计。版图设计从整个设计过程的早期阶段就需要开始考虑,以避免不引入过大的寄生效应以及确保设计的可实现性。功放的第一和第二级使用共同的栅极偏置引线(加在引脚 PA_Vg12 上),而第三级设置单独的偏置引线(PA_Vg3)。这样就可以单独优化两个电压,以对 PA 的线性度或 PAE 进行提升。漏极供电可以类似地通过两个独立的引脚施加+4V 电压在“PA_Vd12”和“PA_Vd3”上,尽管这两个引脚在 PCB 板上是相连的。

SPDT 开关采用串并结构,该设计中的串联和并联分支中集成了多个晶体管以提高线性度 1。晶体管截止时的电容限制了关断状态下器件在高频率处的固有隔离度,在 28GHz 时开关晶体管的隔离度仅为几 dB2。减小晶体管尺寸可以改善固有隔离度,但会增加导通状态下的插入损耗并降低其线性度,因此不是一种可行的选择。这里采取的方法是采用片上电感补偿来改善关断状态隔离度。经过细致设计确保导通状态下具有较低插入损耗,以实现发射通道的高输出功率和接收通道的低噪声系数。开关由一个比特位控制电压“Vctrl1”控制,该位设置为 4V 时表示发射模式、0V 时表示接收模式。“单刀双掷控制电路”(SPDT 控制电路)可实现单比特控制,该电路本质上是一对二线译码器。控制电路和 SPDT 本身消耗的总电流仅 1mA,由“VD_SW”处施加的+4V 电源提供。

接收通道的输入位于通过 SPDT 连接到两级 LNA 输入的“天线”引脚处。接收通道的输出位于标记为“LNA_RFout”的引脚上。与 PA 一样,LNA 也具有快速开关赋能电路,使得 LNA 在不工作时仅消耗低至 0.1mA 的电流。低噪声放大器设计过程的关键是找到一种消耗电流低、又具有良好噪声系数和足够线性度的设计。

重要的第一步是选择合适的晶体管尺寸。可使用多个短叉指来减小晶体管的栅极电阻并改善噪声系数。低噪放的两级都采用了串联感性反馈,以使最佳噪声系数所需的阻抗更接近于共轭匹配和最佳增益所需的阻抗。

低噪声放大器的第一级以噪声系数为设计优化目标,但仍需产生足够的增益才能充分降低第二级噪声系数的影响。低噪放第二级的噪声系数并不重要,因此这级设计成比第一级有更高的增益。设计得到的 LNA 仅需要+4V 电源的 10mA 直流电流。栅极偏置电压施加在引脚“LNA_Vg”上,而+4V 漏极偏置电压加在“LNA_Vd”上。“LNA_Vsense”引脚则提供对偏置电流的监测。监测到的偏置电流信息可以用于控制栅极电压以补偿例如温度等环境条件的变化。在正确偏置下,此监测引脚的电压为 3.9V。使用增强型晶体管的工艺意味着只需要正电源电压,从而使 MMIC 非常便于系统集成。

仔细的电磁仿真对确保各个模块良好的射频性能是非常重要的。采用了逐步添加的方法,每次将电路的一部分加入到 EM 仿真中,而其余部分仍使用工艺设计套件(PDK)中的模型进行仿真。由于集成电路用于二次注塑工艺所得塑料封装中,所以在集成电路上方注塑的化合物也需要在电磁仿真中考虑。

3. 评估和测试

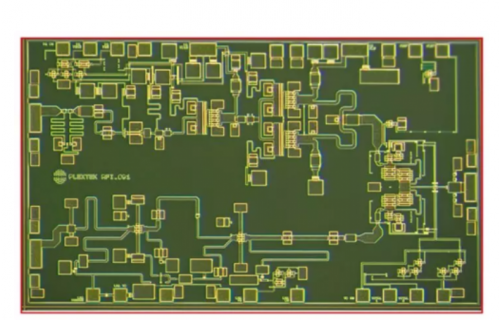

图 3 是射频前端芯片的照片。该射频前端 MMIC 芯片尺寸为 3.38mm × 1.99mm。其焊盘 / 引脚位置与框图中所示的位置相似,并且它还多集成了多个接地盘,以使其完全可以进行在片射频测试(RFOW)。它被设计为采用低成本注塑成型 5mm × 5mmQFN 封装。并且考虑到铸模塑料的影响,需要精心设计从芯片到 PCB 的射频过渡界面。设计了定制的引线框架用于实现该过渡,并且封装体上的射频端口都被设计为接地 - 信号 - 接地(GSG)界面。

图 3:28GHz 5G 通信射频前端模块 MMIC 的芯片照片

完成加工制造之后,对多块芯片进行了在片射频测试,以便在封装之前确认芯片达成了一次流片即成功的设计目标。这里没有给出在片射频测试结果,给出的所有结果都是芯片完整封装后安装在典型 PCB 评估板上后测量得到的。

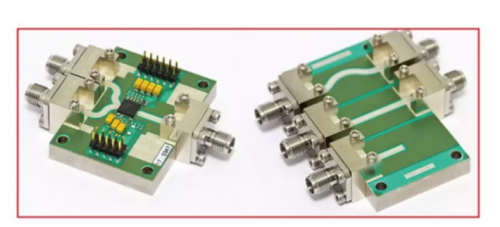

PCB 评估板采用低成本层压板材料设计,适合大批量生产。将封装好的射频前端模块样品组装到 PCB 评估板上;所有测量的性能都校准到 PCB 评估板上的封装引脚处,从而包含了芯片到 PCB 过渡结构的影响。设计了 TRL 校准单元来将测量的性能校准到封装的参考面。图 4 显示了 TRL 校准 PCB 板,以及一块 PCB 评估板的照片。

图 4:封装好的射频前端模块验证板和 TRL 校准板照片

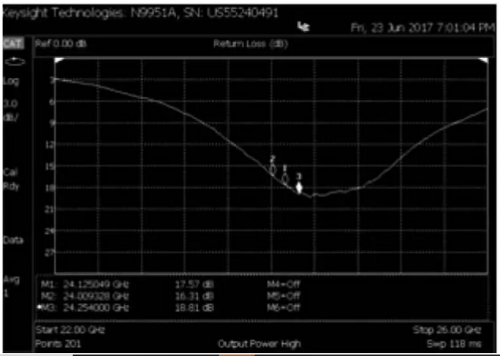

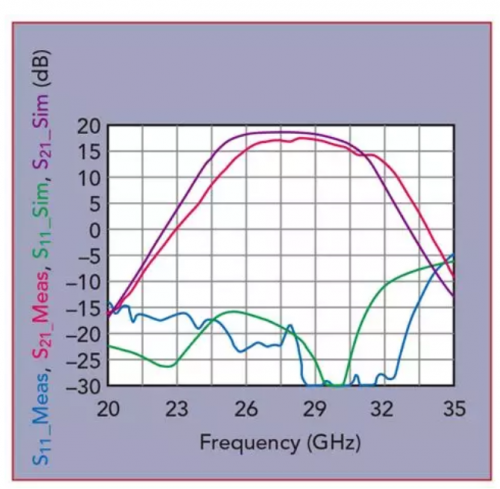

射频前端模块 MMIC 安装在 PCB 上,并以封装的射频引脚为参考面获取验证结果。在验证过程中使用市售的多通道 DAC 和 ADC 芯片来控制和监测射频前端模块。该射频前端模块不需要任何负电压,因为它采用的是增强型工艺。图 5 给出了一个典型射频前端模块的发射通道的测量与仿真 S 参数的比较。测量数据和仿真结果相当吻合。在此模式下,LNA 被关闭,SPDT 控制位“Vctrl1”切换为高电平,而 PA 则偏置在+4V 电压下约 70mA 总静态电流。从 27 到 29GHz,小信号增益(S21)为 17.1dB±0.4dB。输入反射衰减(S11)在整个频段优于 18dB。由于输出匹配是按功率回退条件下最佳 PAE 设计,而不是最好的 S22,尽管如此测量到的 S22(未给出图示)在整个频带上为 8dB 或更好。

图 5:射频前端模块的发射通道的小信号性能测试与仿真对比

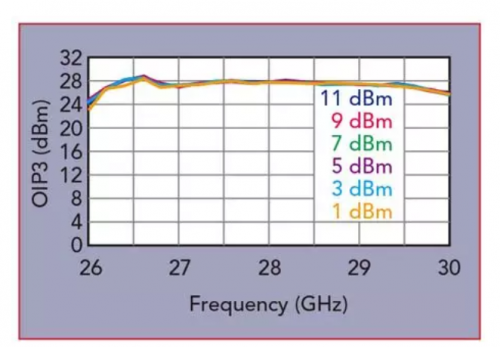

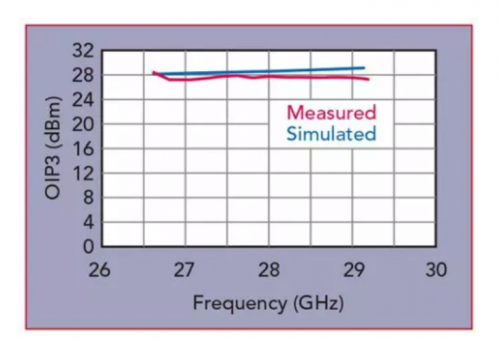

以输出为参考的发射通道的三阶截取点(OIP3)以 100MHz 的频率间隔进行评估,以反映 5G 系统中的宽信道带宽。图 6 是典型射频前端模块的实测 OIP3 与有用频率的功率之间的关系图,其功率范围从 1 至 11dBm。可以看出该 5G 频段上的 OIP3 约为+28dBm,有用频率功率在 10dB 范围内变动时,OIP3 变化很小。测量到的和仿真的 OIP3 与频率的关系如图 7 所示,具有良好的一致性。

图 6:射频前端模块发射通道的 OIP3 与频率和输出功率的关系(100MHz 的频率间隔)

图 7:测得的和仿真的 OIP3 随频率变化的比较

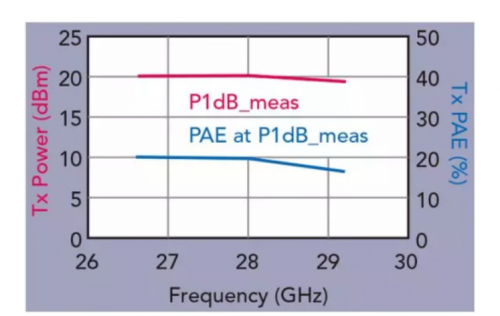

尽管 5G 通信系统需要线性放大来保持调制保真度,但为了提供一个便于比较的性能指标,还是有必要测量输出 P1dB 和 PAE。测量所得性能如图 8 所示,可见 P1dB 在 20.2dBm 左右,并在饱和时上升到 21dBm。FEM 的发射通道 PAE 约为 20%,仅在该频带的高段略有下降。

图 8:发射通道测得的 P1dB 和 PAE 随频率的变化关系

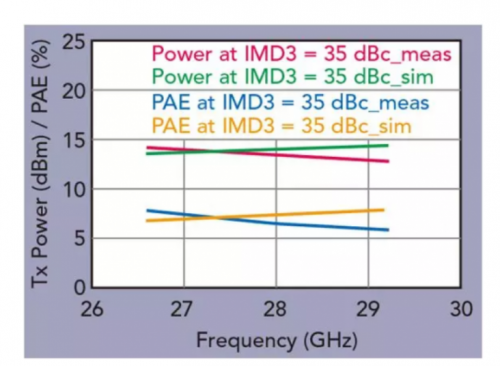

如上所述,该 FEM 的设计是为了实现从 P1dB 回退 7dB 左右时的最佳性能指标(OIP3 和 PAE)。具体指标是在 100MHz 间隔的双频测试中,IMD3(三阶交调项)相对于所需有用信号,要低 -35dBc。这个工作点很接近于该射频前端将用于的 5G 系统的设定要求。

图 9 显示了在 -35dBc 的 IMD3 点工作时,测量和仿真的 PAE 和总射频输出功率的关系图。测得的 PAE 达到较好的 6.5%,主要是由于 PA 被设计工作在深 AB 类。总射频输出功率大约为 13.5dBm,这对应于+28dBm 的 OIP3 功率。

图 9:7dB 功率回退下发射通道测试和仿真所得的功率和 PAE 比较。

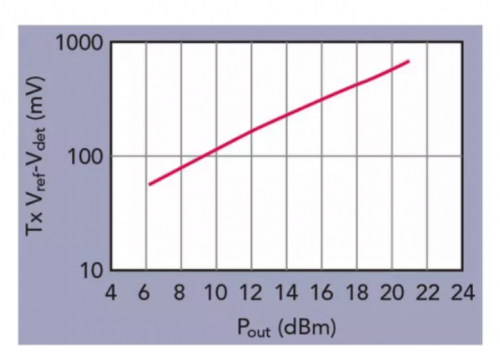

根据片上射频通道功率检测器的特性,可通过一个直流电压监测射频输出功率的大小。图 10 给出了温度补偿检测器输出电压“Vref-Vdet”(mV 为单位,对数坐标)与输出功率(单位 dBm)的关系,包含了超过 15dB 的变化范围。在对数坐标下这个特性关系是线性的,使得功率监测更容易。

图 10:28GHz 时射频前端模块发射通道的片上功率检测器输出特性曲线

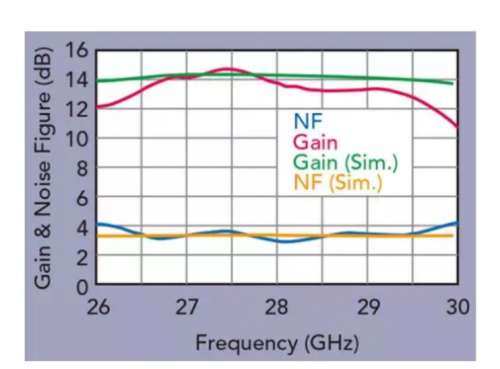

当使用 FEM 的接收通道时,PA 被关闭,“Vctrl1”设置为 0V,LNA 被偏置在+4V 电源下 10mA 左右,此时在“LNA_Vsense”引脚上观察到 3.9V 电压。图 11 给出了测量和仿真增益和噪声系数(NF)的比较。测得的小信号增益约为 13.5dB,整个频段的增益平坦度达到±0.3dB。接收通道具有极佳的噪声系数,从 27 到 29GHz 的典型值为 3.3dB,且仿真和测量到的性能之间具有良好的一致性。

图 11:接收通道测试和仿真所得增益与噪声系数

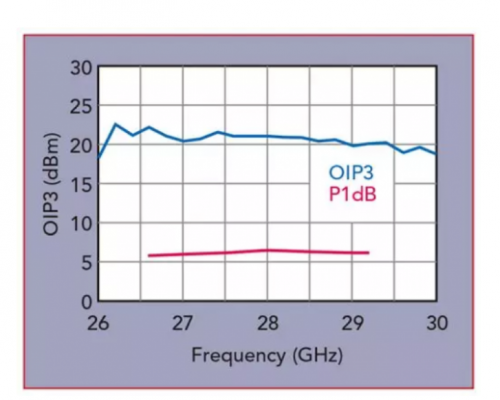

接收通道也具有相当不错的线性度,且只消耗不大的功率(只有 40mW:4V 时 10mA)。诸如 P1dB 和 OIP3 等关键指标在整个频段分别为 6.2 和 21dBm 左右。图 12 是测试所得 P1dB 和 OIP3 随频率变化的关系。

图 12:接收通道测试所得 P1dB 和 OIP3

4. 结论

本文介绍的射频前端 MMIC 将在未来的 28GHz 频段 5G 系统中发挥关键作用。该模块已经验证可以满足集成到毫米波相控阵或波束切换终端的所有要求,并提供卓越的发射通道线性度和效率,同时还有出色的接收噪声系数。发射和接收通道的关键性能指标都达到了设计要求,使得该模块非常适合毫米波 5G 应用。该芯片还包括了多种实用的功能,如发射功率检测器、发射和接收赋能电路,SPDT 译码器电路和接收偏置监测电路。采用最先进的 0.15μm 增强型砷化镓 PHEMT 工艺实现。该模块非常易于使用常见的多通道 ADC 和 DAC 芯片进行控制和监测。此外,该模块可方便地封装在一个紧凑且低成本的 5mm × 5mm QFN 表贴塑料封装中。

登录

登录

注册

注册